# Manufacturing Technology of a Small Capacity Inverter with Fairchild IGBT

Discrete Application Engineering Group, Written by Kee Ju Um, Yeong Joo Kim

### Contents

- 1. Introduction

- 2. How to choose a gate resistance

- 3. Design Technique of Protection Circuit

- 4. Usage of the Gate Drive IC with a Boot Strap Circuit

- 5. Example of an Inverter design with SGP5N60RUFD

- 6. Conclusion

### 1. Introduction

With the active supply of the IGBT, which was used previously only for large power industrial circuits, instances where it is being used in general products are increasing gradually. This is especially true in the household electronics arena where mid-to-small size motors are used and where the products are becoming high-quality and high efficiency in power consumption is demanded. In these aspects, this area is being recognized as a market where the IGBT could be easily applied. The 3<sup>rd</sup> generation IGBT which Fairchild Semiconductors is producing is superior in many aspects. The fact that low tail current at turn off and low saturation voltage at on-state can reduce the IGBT loss is unprecedented and makes it the biggest advantage of many for the Fairchild IGBT. Because of the low tail current feature, the Fairchild IGBT can turn off quickly, reducing the switching loss at high speed operation. This enables the IGBT to be designed in a way such that its switching speed is as fast as possible without need for a separate cooling apparatus. The low saturation voltage reduces the conduction loss, resulting the reduction of the overall power loss. Furthermore, a short circuit rated IGBT can be used easily in variety of application circuits because it can withstand at least  $10[\musec]$  under any short-circuit accidents.

This application note supports the technology which can produce a small capacity inverter using the superior features of the Fairchild IGBT. Starting from the gate drive resistance selection method to cautionary items in PCB design, this application note comprehensively covers all information needed to design a small capacity inverter. Because the inverter to be designed is for household electronics, which need cost reductions, this application note focuses on how to form an low cost inverter. Section 2 of this note details the items which must be considered when deciding on the gate resistance and Section 3 deals with general items in the small capacity inverter related to driving the motor and describes the over-current protection design in the inverter appropriate for driving the motor and the short circuit protection circuit to protect the IGBT, used. Section 4 introduces the boot strap used often in the inverter gate drive; it also details the method for deciding on the value of each component. These values can be used in other application circuits. Lastly, in Section 5 designs an actual 3[kVA] class inverter based on the information discussed in the previous sections.

### 2. How to choose a gate resistance

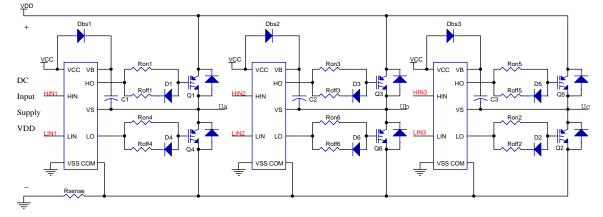

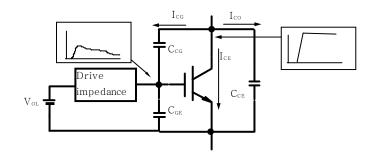

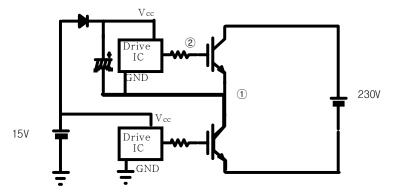

The following figure is the output circuitry of the Fairchild inverter to be designed in this application note.

### Figure 2.1 Output Circuitry of the Fairchild Inverter

Normally, the inverter gate resistance is designed by separating it into the turn-on resistance (Ron) and the turn-off resistance (Roff), as shown in Figure 2.1. The selection methods for each resistance are in respect to the gate drive IC and to the IGBT, respectively. The value of the gate resistance can be selected from the intersection of the possible gate drive resistance range with respect to these two methods.

#### 2.1 Selection of the Resistance Value Considering the Gate Drive IC Drive Capability

The magnitude of the gate resistance,  $R_G$ , connected to the gate drive IC output is determined based on the peak current ( $I_{ON}$ ,  $I_{OFF,PEAK}$ ) which is charged and discharged between the gate and the emitter. The maximum current which can electrically charge the gate oxide between the gate and the emitter is determined based on the maximum source current of the gate drive IC. On the other hand, the maximum current which can discharge the gate oxide can is determined based on the maximum sink current of the gate drive IC. The minimum gate resistance value,  $R_G$ , is, in turn, determined based on these determined maximum charge and discharge currents.

### Determination of the Minimum R<sub>G</sub> Based on the Maximum Drive Capability of the Gate Drive IC

If we assume that the equivalent capacitor ( $C_{GE}$ ) between the IGBT emitter and gate has discharged to the gate drive turn off voltage ( $V_{OL}$ ) to obtain the minimum value of the turn on resistance  $R_{ON}$  and that the capacitor has charged to the gate drive turn on voltage ( $V_{OH}$ ) to obtain the minimum value of the turn off resistance  $R_{OFE}$ , the following relationships can be derived from the Ohm's Law.

$$R_{ON}^{MIN} = \frac{V_{OH} - V_{OL}}{I_{SOURCE}^{MAX}} \text{ and } R_{OFF}^{MIN} = \frac{V_{OH} - V_{OL}}{I_{SINK}^{MAX}}$$

(1)

where

$R_{ON}^{MIN}$  = minimum value of the turn on resistance,

$R_{OFF}^{MIN}$  = minimum value of the turn off resistance,

V<sub>OH</sub> = turn on output maximum voltage of the gate drive IC

V<sub>OL</sub> = turn off output minimum voltage of the gate drive IC

$I_{SOURCE}^{MAX}$  = maximum output source current of the gate drive IC

$I_{SINK}^{MAX}$  = maximum output sink current of the gate drive IC

Because the maximum sink current is greater than the source current generally in the gate drive IC output, generally, (Imax-source<I max-sink), the selected gate resistance must be greater than R<sup>MIN</sup><sub>ON</sub> if the turn on and turn off resistances are not separated and used as one.

#### Calculation of the Power Loss in the Gate Drive IC

The total power loss  $(P_T)$  in the gate drive can be calculated from the following equation.

$$P_{T} = P_{BIAS} + P_{SWITCH}$$

=  $I_{CC}V_{CC} + I_{EE}V_{EE} + E_{SWITCH}f_{SWITCH}$  (2)

#### where,

P<sub>BIAS</sub>: power consumed to bias the elements in the IC in normal state

P<sub>SWITCH</sub>: Switching loss associated with turning on and off the IGBT gate

$\mathsf{E}_{\mathsf{SWITCH}}$ : Average loss (uJ/cycle)in the IC during one cycle of turning on and off.

f<sub>SWITCH</sub>: Average turn off frequency

V<sub>CC</sub>: + power supply voltage

V<sub>EE</sub>: - power supply voltage

$I_{CC}$ : Average + power supply current in normal state

I<sub>FF</sub>: Average - power supply current in normal state

If the gate resistance is lowered, the E<sub>SWITCH</sub> value increases and, if the switching speed is increased, P<sub>SWITCH</sub> increases. The total power loss calculated from the above equation should not exceed the maximum value identified in the databook.

#### 2.2 Selection of the Resistance value considering the IGBT Drive Conditions

#### The relationship between the switching loss and the gate resistance

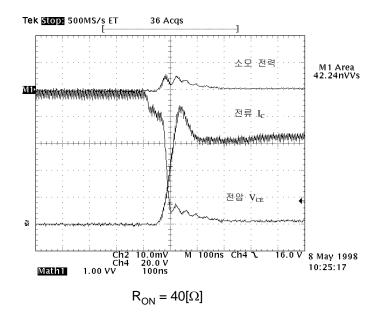

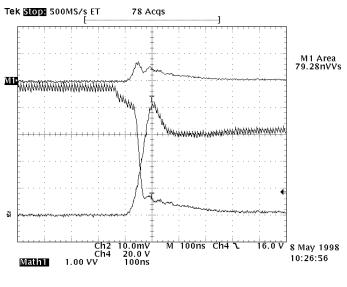

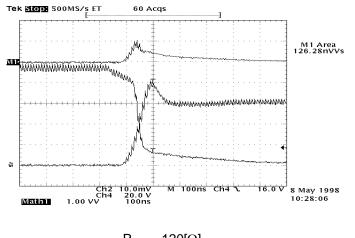

The IGBT internal is such that the MOSFET driven by the gate turns on the output bipolar TR. Because the determined maximum current between the drain and source of the MOSFET is proportional to the gate voltage, the IGBT turn on characteristic is affected by the magnitude of the voltage and current applied to the gate. This turn on characteristic significantly affects the IGBT turn on loss. Therefore, if the magnitude of the turn on resistance is reduced, the internal MOSFET turns on quickly, and, as a result, the switching loss also reduces. The following figure shows each of the waveforms which are turned on when the gate resistance is changed in the Fairchild IGBT, SGP5N60RUFD.

Test Condition: L = 78[

$$\mu$$

H], R = 21.2[ $\Omega$ ], T = 25[ $^{\circ}$ C], V<sub>OH</sub> = 15[V]

$$V_{CC} = 80[V] (20V/DIV), I_{C} = 3[A] (1A/DIV)$$

Figure 2.2

$\mathsf{R}_{\mathsf{ON}} = 80[\Omega]$

Figure 2.2 Turn on Waveforms of SGP5N60RUFD when the Gate Resistance is changed.

The following table summarizes the turn on losses measured from the above tests. The areas of the waveforms for the consumed power, above, were converted to the power loss values used in the table.

| _ |                     |      |      |      |       |       |  |

|---|---------------------|------|------|------|-------|-------|--|

|   | R <sub>ON</sub> (Ω) | 40   | 60   | 80   | 100   | 120   |  |

|   | Loss (µJ)           | 4.22 | 5.62 | 7.93 | 11.04 | 12.63 |  |

### SGP5N60RUFD

#### SGP10N60RUFD

| R <sub>ON</sub> (Ω) | 40   | 60   | 80   | 100  | 120  |

|---------------------|------|------|------|------|------|

| Loss (µJ)           | 3.16 | 3.58 | 4.73 | 5.31 | 6.44 |

#### Table 2.1 Relationship between the Turn on Loss and Gate Resistance

The figures and tables above reveal that turn on losses reduces as the gate resistance is increased. The turn off speed is affected more by the minority carrier recombination mechanism, an inherent feature of the IGBT output bipolar TR, than by the MOSFET turn off speed; therefore, there is relatively a small relationship between magnitude of the gate resistance and the turn off speed. However, if the gate resistance increases above a specific value, the turn off speed becomes affected more by the internal MOSFET turn off time than by the minority carrier recombination time, reducing the IGBT turn off speed and, in turn, increasing the turn off loss. Therefore, the discharge resistance must be maintained below an appropriate value. The following table summarizes the turn off loss under the same test conditions as the turn on test.

#### SGP5N60RUFD

| R <sub>ON</sub> (Ω) | 40   | 60   | 80   | 100  | 120  |

|---------------------|------|------|------|------|------|

| Loss (µJ)           | 65.9 | 65.9 | 66.2 | 66.4 | 67.2 |

#### SGP10N60RUFD

| R <sub>ON</sub> (Ω) | 40   | 60   | 80   | 100  | 120  |

|---------------------|------|------|------|------|------|

| Loss (µJ)           | 45.9 | 45.9 | 47.3 | 47.3 | 49.8 |

#### Table 2.2 Relationship between the Turn off Loss and Gate Resistance

There is almost no change in the turn off loss with change in the gate resistance.

#### Relationship between the Gate Resistance and dv/dt Sensitivity

Figure 2.5 Equivalent Circuit Depicting a Gate which Turns on Based on the dv/dt

IGBTs, as shown in Figure 2.2, have individual capacitances between the emitter and the gate and between the gate and the collector. The capacitance,  $C_{ge}$ , between the emitter and the gate and the capacitance,  $C_{gc}$ , called the Miller capacitance between the gate and the collector play important roles. Not only does the Miller capacitance like the Miller effect delay the IGBT turn on time, but it also allows in the current of  $R_{OFF} \leq \frac{dv}{dt}$  to flow in when there is a sudden change in the voltage between the emitter and collector,

producing a voltage of  $R_{OFF} C_{gc} \frac{dv}{dt} - V_{OL}$  at the gate. The moment that this voltage becomes greater than the minimum voltage needed to turn on the gate,  $V_{TH}$ , the IGBT turns on, causing an accident similar to a short circuit. Accordingly, the minimum gate off resistance value can be obtained from the following quation.

$$R_{OFF} \leq \frac{V_{TH} + V_{OL}}{C_{gc} \frac{dv}{dt}}$$

(3)

If the gate turn off voltage,  $V_{OL}$ , is negative or is large,  $R_{OFF}$  could become sufficiently large.

## Relationship between the Gate Resistance and the Freewheel Peak Diode Recovery Current and Diode Inrush Current

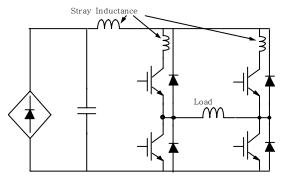

The following figure shows the stray inductance which always exists in the circuit.

Figure 2.6 Figure Showing the Stray Inductance in the Circuit

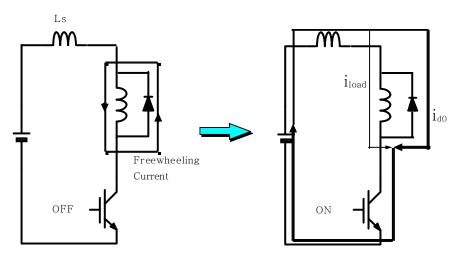

The above diagram is simplified into the diagrams below to explain the freewheel diode peak recovery voltage.

Figure 2.7 Figure Showing the Recovery Current Flow in the Diode

When an off IGBT is turned on abruptly while the diode is operating in one way, an instantaneous current flows through the diode until the diode PN junction voltage is recovered; this is shown in the above figure.

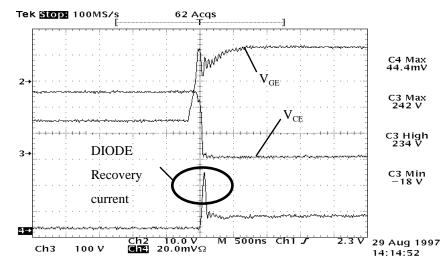

Figure 2.8 Figure Showing the Diode Recovery Current Flow ( $R_{ON}$ =0[ $\Omega$ ], L=48[mH]

Though the current amount is not big enough to destroy the IGBT, the instantaneous current slope becomes steep. This type of an abrupt slope generates a voltage  $L_S \frac{di_{do}}{dt}$  of in the stray inductance in the circuit of Figure 2.7. This voltage resonates with the stray capacitance in the circuit to produce oscillation similar to the V<sub>GE</sub> waveform in Figure 2.8 or to cause EMI problems. If the gate resistance is increased at this time, the diode recovery current slope of  $\frac{di_{do}}{dt}$  reduces the occurrence of these phenomena, making them less frequent. Because the peak voltage, generated by the diode recovery current, is different depending on the stray inductance, it is very difficult to correctly calculate its value through an equation;

therefore, it would be better to determine its minimum value based on the gate resistance through repeated testing.

### 3. Design Technique of a Protection Circuit

Because an inverter is a circuit which delivers power, the entire circuit becomes damaged due to the large current that flows when accidents such as a short circuit occurs. This type of an accident can lead to a fire, which can be prevented with the insertion of a current protection circuit. Though general household electronics can block an over current or short circuit current through a current fuse or the like, this type of fuse or similar methods cannot protect the IGBT or similar semiconductor switching components because they deteriorate faster than the time required by the fuse to cutoff the current. The Fairchild IGBT must cutoff the current at most  $1.5[\mu sec]$  beforehand after a short circuit has occurred for a product with no short circuit current measures and within 20 [ $\mu sec$ ] even for a product with short circuit current measures to protect the IGBT in both cases. This section reviews the method of designing a protection circuit which can safely

protect the IGBT against an over-current or short circuit.

#### 3.1 Current Sensing Method

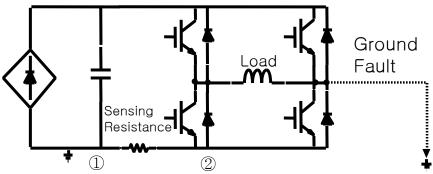

Though there are many methods of sensing the current flowing in the general IGBT (not the sense IGBT for current sensing), a detection resistance inserted at the DC link terminal is the most widely used method, as

shown in the figure below.

Figure 3.1 Current Sensing Resistance Inserted at the DC Link Terminal

As shown by the above figure, the sensing resistance must be inserted after the smoothing capacitor . Because power is consumed through this resistance even at normal conditions, it cannot be used in the inverters which use large current amounts. It is used widely in common, small capacity inverters. The resistance insertion method can sense the entire current at one place and, thus, one protection circuit can protect the entire IGBT. Though this feature, which reduces the inverter production cost, is an advantage, the fact that the protection circuit can fail when a large current ground accident occurs in which the current does not flow through the resistance, as depicted in figure 3.1, is a disadvantage.

Furthermore, when there is large amount of current flowing, differential potential appears across the resistance due the current. This increases the potential at 1) the ground of figure 3.1 and at 2) the emitter terminal of the lower IGBT and the gate drive circuit ground. Therefore, the gate drive circuit should be designed considering this potential increase. For example, if the potential at 2) increases 2V when using a gate drive IC with an input threshold of 2V, a voltage over 4V must be applied at the input to exceed the threshold voltage. For this reason, a protection circuit is inserted in all IGBT gate drive block in most large capacity inverters. By sensing each of the  $V_{CE}$  saturation voltage of the IGBT, the protection circuit operates individually when the  $V_{CE}$  saturation voltage exceeds a specific voltage.

The size of the sensing resistance inserted at the DC link terminal is selected according to the mechanism using the inverter. For example, about  $0.2[\Omega]$  low inductance resister is used usually for a  $1\sim2[A]$  capacity inverter and about  $0.1[\Omega]$  for a  $3\sim4[A]$  capacity inverter. However, for inverter capacity over 10[A], it is best not to use this method because accuracy falls for any lower resistance. Because the voltage across the resistance is quite low when the inverter is operating normally and the noise of the power source from the chopping frequency is detected, the following filter circuit must be used in over-current sensing circuit, which has a low detection level. The low pass filter used in the over-current sensing circuit is closely related to the over-current protection circuit; this will be reviewed again in Section 3.2.

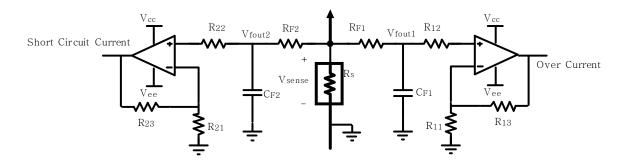

Figure 3.2 The Circuit that Amplifies the Detection Voltage

The relationship between the input voltage  $V_{\text{SENSE}}$  and output voltage  $V_{\text{FOUT}}$  of the low pass filter is presented in the following equation.

$$V_{FOUT} = \frac{\frac{1}{R_F C_F}}{S + \frac{1}{R_F C_F}} V_{SENSE}$$

(4)

The filter  $1/R_{F1}C_{F1}$  constant required for over-current sensing must be smaller than the filter constant  $1/R_{F2}C_{F2}$  required for short current detection. In other words, the filter response speed needed for short current detection must be fast.

The amplification gain of the amplifier and resistance calculation of R<sub>12</sub> (I=1, 2), are shown below.

$$V_{CO} = \frac{R_{i1} + R_{\beta}}{R_{i1}} \cdot V_{FOUT}, R_{i2} = \frac{R_{i1} + R_{\beta}}{R_{i1} + R_{\beta}}, \quad (I = 1, 2)$$

(5)

A non-inverting amplifier was used to amplify the input impedance. Therefore, the output of the amplifier, V<sub>CO</sub>, is usually positive, but it can be negative when regenerating to the voltage source during the freewheeling. If the output absolutely needs to be positive in such a case, a rectified circuit must be added at the output. If freewheeling which converts to the power source does not exist, does not become negative and a rectified circuit does not need to be considered. Because the IGBT must be turned off within 20[sec] after a short circuit, the gate cutoff signal must leave the filter input within 20[sec]. However, there are many instances when this 20[sec] cannot be met due to the differences in the LPF designs. In such instances, the detection must be done before the 20[sec] by controlling the amplifier gain and comparator detection level. The filter design will be reviewed in detail in the actual inverter design in Section 5.

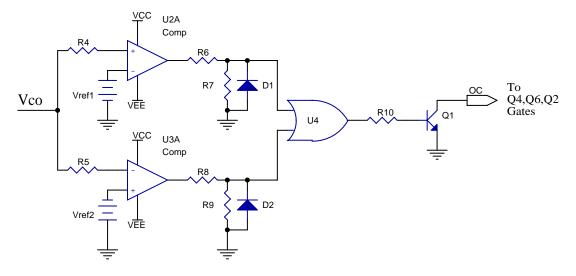

#### 3.2 Over-Current Protection Circuit

There are many over-current protection methods depending on the mechanism to which the inverter is applied. This application note designs a smoothly operating the over-current protection circuit for an inverter applied to a BLDC motor. The following is a diagram of the over-current protection circuit.

When a specific level of over-current is detected initially, the above over-current protection circuit is designed to physically cutoff the bottom gate but recover the gate completely after a specific delay time. Furthermore, it was designed to take into account a negative current during the regenerative breaking of the motor and to have diodes (D1, D2) inserted at the comparator output terminal to block the comparator output from becoming negative. When a over-current is detected, it operates from the OR gate through  $R_{10}$  to drive the TR. The base current,  $i_B$ , is determined based on the value of resistance,  $R_{10}$ , and maximum current •

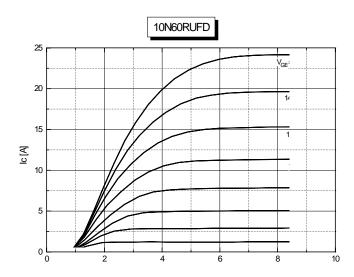

$I = H_{FE}$  i<sub>B</sub> of flows through TR. At this time, the potential of the IGBT gate is determined based on the voltage of the gate drive IC output, the value of the resistance, R<sub>10</sub>, and the value of the turn off resistance, R<sub>OFF</sub>. The following figure shows the relationship between the IGBT emitter gate voltage, V<sub>GE</sub>, and the maximum current that can flow in the IGBT.

Figure 3.4.1 The Relationship between V<sub>GE</sub> and the Maximum Current that can flow in the IGBT (5N60RUFD)

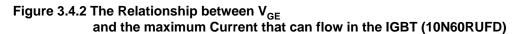

As shown in the above figure, if the gate voltage is not dropped completely to 0[V] but to an appropriate level of (6–7[V]), the IGBT current reduces to 2–3[A]. Furthermore, if the cutoff TR gate resistance,  $R_{10}$ , is selected appropriately, a comparatively smooth cutoff waveform can be obtained. The following figure shows the protection circuit operation when an over-current flows in the inverter.

Figure 3.5 Over-current Protection Circuit Operation

The turn off interval,  $T_{DOFF}$ , as shown in the above figure is the most important constant in the actual operation of the over-current protection circuit. If  $T_{DOFF}$  is too short, high speed switching can occur during an over-current and the IGBT can be thermally destroyed and, if it is too long, an interval where the current is dis-continuous can arise, enlarging the current ripple which appears as the motor torque ripple.

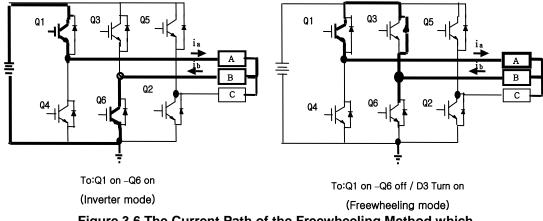

Therefore, T<sub>DOFF</sub> is determined separately from the current reduction slope at turn off. Most motors have inductive elements inside and all inverter circuits have freewheeling paths to make the current flow continuously in these inductive elements. The current reduction slope at turn off varies greatly with the size of the inductive resistance in the motor and with the freewheeling method. Freewheeling method can be divided into that which turns off both the IGBT top and lower terminals and that which turns off either only the top or bottom terminal. The following figure shows the current path of the former method, which turns off

both the top and bottom IGBT.

## Figure 3.6 The Current Path of the Freewheeling Method which turns off both the top and bottom parts of the IGBT

As shown in Fig. 3.6, the freewheeling current flows reverse through the opposite diode to the IGBT which was turned on just before in the same arms. The equation for freewheeling in the circuit is presented below.

$$L_{a}\frac{di_{f}}{dt} + R_{a}i_{f} = -E$$

(6)

Here,  $L_a$  is sum of all the inductive resistances;  $R_a$  is the sum of all the resistances in the circuit;  $i_f$  is the freewheeling current; and E is the power source voltage. If the initial current when the turn off starts is  $i_o$ , the

freewheeling current can be obtained from the following equation.

$$i_{f}(t) = i_{o} e^{\frac{Ra}{La}t} - \frac{E}{R} \left[ 1 - e^{\frac{Ra}{La}t} \right], i_{f}(t) \ge 0$$

$$(7)$$

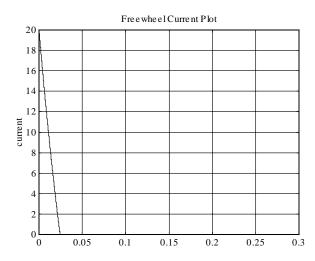

If we note the direction of the freewheeling current as +, the current continues to reduce until it becomes 0 and, when it becomes negative, the diode stops the current. The fact that the current reduces quickly as the power source voltage, E, increases is revealed in the above equation. The following figure graphs the current when the power voltage is 200[V], resistance,  $5[\Omega]$ , inductive components, 300[mH], and initial current, 20[A].

Figure 3.7 Waveform of the Freewheeling Current of the Method which turns of Both the Top and Bottom Parts of the IGBT

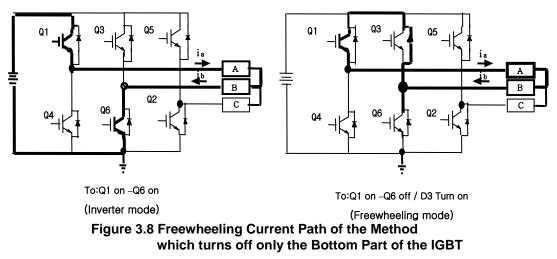

The above figure reveals the abrupt drop of the current. The figure below shows the freewheeling path when only the bottom part of the IGBT is turned off.

The freewheeling current flows through the diode opposite the bottom part of the IGBT which was on and the top part of the IGBT. The equation for the freewheeling in the circuit is presented below.

$$L_{a}\frac{di_{f}}{dt} + R_{a}i_{f} = 0$$

(8)

If the initial current at the start of the turn off is  $i_0$ , the current can be obtained as follows:

$$i_{f}(t) = i_{o} e^{-\frac{Ra}{La}t}$$

(9)

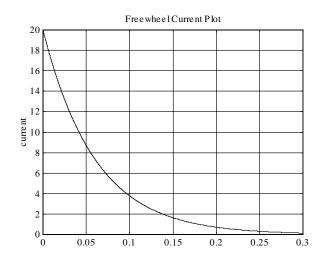

The current waveform of a circuit with the above freewheeling path and coefficient in Figure 3.7 is presented below.

#### Figure 3.9 Freewheeling Current Waveform of the Method which turns off the Entire Bottom Part of the IGBT

Comparison of Figure 3.7 with 3.8 reveals that turning off both the top and bottom brings about much faster decrease.  $T_{DOFF}$  must be shorten to reduce the the ripple of the current with the fast decrease, but switching the component too quickly can heat the component severely when the current is becoming an over-current and has a negative effect on the component's metal characteristics. Therefore, this application note supports the method which reduces the current by switching only the bottom part of the IGBT.

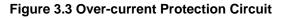

#### 3.3 Short Circuit Current Protection Circuit

When an accident such as an inverter Arm Short or Shoot Through is generated, the current suddenly increases at a sharp slope, saturating the IGBT with the maximum allowable current, as in Figure 3.4. The Fairchild IGBT (Short Circuit Rated IGBT), which account for short circuit currents, can withstand such an accident for  $20[\mu$ sec]. If the IGBT is turned off within this time, the IGBT can be protected from damage. In a 5 [A] IGBT, the short circuit current protection operates normally around 10[A]. If it increases the current gradually, the over-current protection circuit set at 7[A] starts to operate first, preventing the current from reaching the short circuit current specified value. However, because the current increases with a sharp slope in a short circuit with a relatively slow response speed initiates the over-current protection circuit. A current that can destroy the IGBT instantly flows through the circuit when there is a short circuit current. Therefore, if it cuts off the current instantaneously and continues to repeat the operation like the over-current protection circuit, the IGBT heats up instantaneously, bring about a thermal latch-up state. Even if the IGBT cuts off the gate signal working like a thyristor in this condition, the IGBT is unable to turn off and becomes damaged. Therefore, the short circuit current protection must cutoff the gate when a short circuit is detected until the reset signal enters from outside.

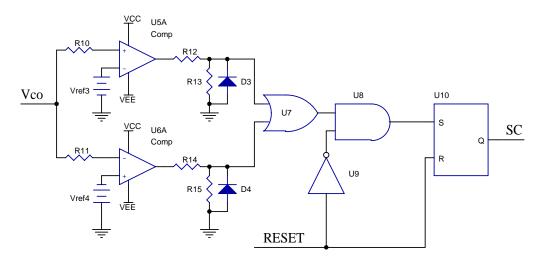

Figure 3.10 Short Circuit Current Protection Circuit

The RS F/F operation used as the latch circuit in the above circuit is presented in the following table.

| R | S | Q <sub>n</sub>   |

|---|---|------------------|

| 0 | 0 | Q <sub>n-1</sub> |

| 0 | 1 | 0                |

| 1 | 0 | 1                |

| 1 | 1 | 1                |

#### Table 3.1 RS F/F Operation Truth Table

The turn off speed must be considered in the short circuit current protection circuit. As mentioned in section 2.2, the current slope generates the circuit surge voltage, according to the stray inductance in the circuit. Unlike the slope of the diode recovery current which could not generate a large voltage, the short circuit current fall from a large current value to 0. For this reason, if the gate voltage is eliminated suddenly at short circuit, the current will have a large slope. If the stray inductance in the circuit is large, a high voltage is generated here. This generated voltage instantaneously will exceed the IGBT surrendering voltage depending on the circuits and will destroy the IGBT at this time. Two types of short circuits are explained below.

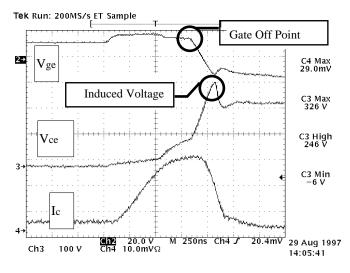

#### Type I: Short Circuit that occurs when the IGBT is working and the current is flowing

This is a situation when a short circuit occurs while a current is flowing in the load for any reason. At this time, the IGBT has been working and the voltage across the IGBT collector and emitter is maintained at about 2[V], as shown in the figure below. If a short circuit occurs, the current abruptly increases to reach the maximum value. If the gate is cutoff at this time,  $V_{CE}$  increases and becomes the same as the power source voltage while the current gradually decreases. At this time, the voltage is generated with the slope of the current, but, because the IGBT voltage is low at initial short circuit, it is rare for the IGBT to be destroyed from such a short circuit, unless the voltage was generated extremely large.

IGBT: SGH30N60RUFD, DC link voltage: 240[V], Peak Current: 140[A], Stray Inductance: 150[nH]

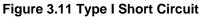

## Type II: The turn on signal is applied to the gate when the IGBT is off and a short circuit has occur in the load

In this case, the  $V_{CE}$  is the same as the power source voltage because the IGBT is off, initially. Because the current started to flow with a sharp slope, the current already reached its maximum before the voltage

across the IGBT has yet to drop, as shown by the figure below.

IGBT: SGH30N60RUFD, DC link voltage: 240[V], Peak Current: 140[A], Stray Inductance: 150[nH]

If the current is cutoff in this situation and the surge voltage is generated, the voltage across the component increases sharply because the  $V_{CE}$  already is already large. If this voltage across the component exceeds the IGBT surrender voltage, it will destroy the IGBT. If the IGBT is destroyed, the gate, emitter and collector all become short circuited and a large current leaks into the drive circuit through the gate, destroying the gate drive IC and damaging its connected power source. Therefore, the inverter should be designed considering the type II accident, being more severe than the type I accident. Because the inverter design with stray inductance, is dealt with in Section 5, the rules of designing a low, turn off slope of the short circuit current will be explained here.

A large capacity inverter cuts off the gate drive voltage by dividing it into 2-step potentials executes the turn off operation due to a short circuit or drops the gate voltage at a slope lower than the usual to prevent sudden current changes. However, because the short circuit current, itself, is small in a small capacity inverter, the slope is also small. Therefore, the turn off slope is controlled by appropriately controlling the gate turn off resistance than through this type of gate operation. Essentially, if the gate turn off resistance is made large, the peak current increases because the charge at the gate could not be quickly extracted and the slope of the decreasing current decreases and, if the resistance is made small, the peak current can be reduced, but the current slope increases. The Fairchild IGBT, which considered the short circuit current, can withstand up to 20 [ $\mu$ sec]. The gate resistance does not need to be reduced to reduce the peak current because it is limited by the inherent characteristics of the IGBT. Therefore, if the stray inductance in the circuit is large, a comparatively large turn off resistance should be selected, and, if small, a small resistance should be selected.

The following table summarizes the gate resistance selection method of Section 2 and the rules for deciding

| Condition      | Increase R <sub>on</sub> | Condition         | Increase R <sub>off</sub> |

|----------------|--------------------------|-------------------|---------------------------|

| Turn on di/dt  | Turn on di/dt            | Turn off loss     | Limited Increase          |

| Turn on loss   | Turn on loss             | Turn off delay    | Increase                  |

|                | Increase                 | Voltage Increase  | Increase                  |

| Turn on time   |                          | time              |                           |

| Diode Recovery | Decrease                 | Current Decrease  | Decrease                  |

| Current        |                          | Time              |                           |

| Diode Recovery | decrease                 | S/C Time          | decrease                  |

| Current        |                          |                   |                           |

| EMI            | Decrease                 | S/C Current Peak  | Decrease                  |

| S/C Time       | Not Applicable           | S/C Voltage Peak  | Not Applicable            |

| S/C Peak       | Not Applicable           | dv/dt Sensitivity | Not Applicable            |

on the gate resistance presented in this paragraph.

Table 3. 2 IGBT Operation according to the gate resistance

### 4. Usage of the Gate Drive IC with a Boot Strap Circuit

A bootstrap circuit uses its own signals etc. to operate the circuit. It is also a circuit which controls the impedance by applying a positive feedback in the general OP amp circuit. In this application note, it supplies the IC power to drive the top IGBT gate by using a diode, capacitor and IGBT switching without making a separate power source on the outside.

#### 4.1 Principle of the Bootstrap Circuit

The following figure represents a bootstrap circuit which uses a diode and a capacitor.

Figure 4.1 An example of a Bootstrap Circuit

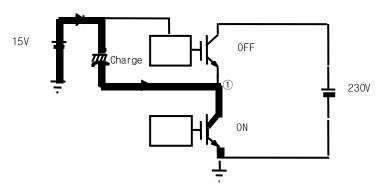

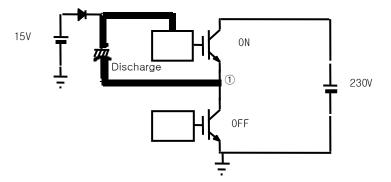

When the IGBT arm as shown in Figure 4.1 is driven, the potential of the inverter output, 1) varies from the ground voltage to the DC link voltage, 230[V]. Essentially, this means that if the top part of the IGBT turns on and the bottom part of the IGBT turns off, the potential at 1) increases to 230[V] but, if the bottom part of the IGBT turns on and the top part of the IGBT turns off, the potential at 1), falls to ground potential. However, to turn on the top part of the IGBT, the potential at 2) must be 15[V] higher than the potential at 1). The potential difference between 1), 2), must be maintained above 15[V], regardless of the absolute potential at 1). For this, the bootstrap circuit (Level Shifter) is used. The bootstrap circuit uses the switching of the bottom part of the IGBT to supply 15V to the top gate drive IC through the diode and capacitor.

Figure 4.2.1 Bootstrap Circuit Operation (Capacitor Charging Mode)

Figure 4.2.2 Bootstrap Circuit Operation (Power Supply Mode)

In Figure 4.2.1, the bottom IGBT turns on first and the potential at 1) drops to ground, turning on the boot strap diode in one direction, which charges the capacitor to 15[V]. In Figure 4.2.2, the bottom part of the IGBT turns off and the top part of the IC operates through the charging in figure 4.2.1 operation. This turns on the top part of the IGBT and, as a result, the potential at 1) becomes 230[V]. Then, the diode turns off in the reverse direction and the capacitor supplies the power to keep the top part of the gate on. As revealed by Figures 4.2.1 and 4.2.2, the gate drive system with the bootstrap configuration must turn on the bottom IGBT first and then turn on the top IGBT to charge the energy to drive the top gate drive in the

#### capacitor. 4.2 Bootstrap Circuit Capacitor Value Determination Method

In a bootstrap circuit, the capacitor supplies the gate energy to turn on the top part of the IGBT. Therefore, a comparatively small capacitor can be used because the charging frequency of the capacitor increases as much as the rapidity of the top/bottom alternate switching speed. On the other hand, if the switching speed is slow, that much of a large capacitor must be used. The size of this type of a capacitor is closely related to the IGBT on/off frequency and voltage applied to the capacitor. The equation below calculates the minimum charge the bootstrap capacitor must supply.

$$Q_{bs} = 2Q_g + [I_{qbs(max)} + I_{cbs(leak)} + I_{bds(leak)} + I_{c(max)}]t_{on}$$

(10)

where

Q<sub>a</sub>: Charge amount of the gate at the top part of the IGBT

t<sub>on</sub>: Turn on time

I<sub>gbs(max)</sub>: Current required to keep the IGBT on

I<sub>cbs(leak)</sub>: Capacitor leakage current

I<sub>dbs(leak)</sub>: Diode reverse leakage current

$I_{c(max)}$ : Maximum current consumed to drive the gate drive IC

The bootstrap capacitor capacity selected should be such that it supplies sufficient charge to the top part of the IGBT, which operates for a long time. The capacity of the bootstrap capacitor is calculated as follows:

$$C \ge \frac{20Q_{bs}}{V_{CC} - V_{f} - V_{ls} - V_{min}}$$

(11)

where,

V<sub>f</sub> = Bootstrap diode one way voltage drop

$V_{ls}$  = Bottom part of the IGBT one way voltage drop

V<sub>min</sub> = Minimum voltage required to turn on the IGBT

In the Samsung IGBT, the leak current between the gate and source or the reverse leakage current of the diode is lower than 100 [mA] and can be ignored. Furthermore, the following equation calculates only the charge to turn on the IGBT and the current to keep the IGBT on.

$$C \ge \frac{2(2Q_{g} + I_{qbs} \cdot t_{on} + I_{c(max)})}{V_{CC} - V_{f} - V_{Is} - V_{min}}$$

(11)

If the recommended, minimum capacitor value calculated in equation (11) to keep the IGBT on is used in an actual application circuit, the generated voltage ripple has a negative effect on the inverter operation. Therefore, the bigger the capacitor value, the better . However, the capacitor about 15~20 times the value calculated from equation (11) can be selected.

#### 4.3 Bootstrap Circuit Diode Selection Method

When the top part of the IGBT is on, almost all the DC link voltage is applied across the bootstrap diode. Therefore, the breakdown voltage of the diode must exceed the minimum DC link voltage at least and must have a fast reverse recovery speed to block the emission of the capacitor charge. A component which minimizes the diode reverse leakage current must be chosen for an application circuit with a comparatively long turn on time. The absolute rating of the diode which satisfies these characteristics is presented in the following equation.

$$\begin{split} &V_{\text{RRM}} \geq \text{DC Link voltage} \\ &t_{\text{rr(max)}} \leq 100\text{ns (typically)} \\ &I_{\text{F}} = Q_{\text{bs}} \boldsymbol{\cdot} \text{ f, where is the operating frequency} \end{split}$$

### 5. A Example of the Inverter design with SGP5N60RUFD

A Fairchild inverter which uses an IGBT which considered the 600[V] 5[A] COPAK short circuit current appropriate for the motor is designed.

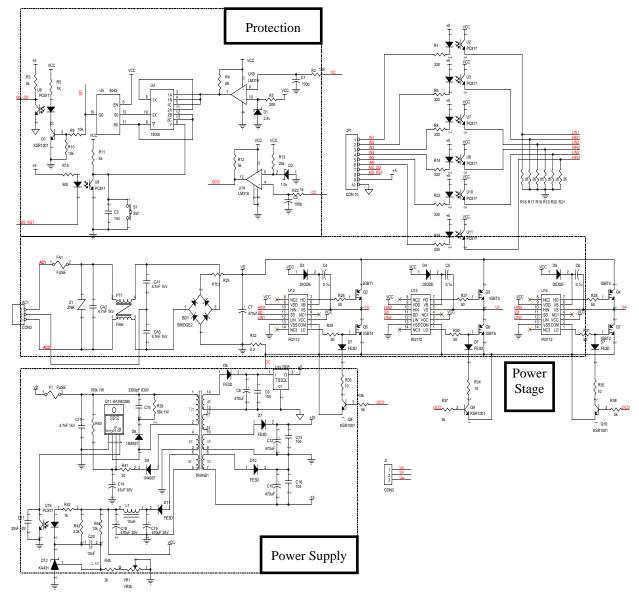

5.1 Circuit Diagram of the Entire System

The circuit diagram of the actual, designed system is shown in the following diagram.

Figure 5.1 Complete Circuit Diagram of the 600[V] 5[A] Inverter

The designed inverter can be divided into the power supply block, power drive block and the protection circuit block. First, the power supply block provides power to the inverter circuit having a gate drive IC using the SMPS (Switching Mode Power Supply) to make the disconnected power supply. In the above diagram, the power supply uses the SPS (Fairchild Power Switch), a Fairchild IC, appropriate for the SMPS. Generally, a large capacity Fairchild inverter must have a power supply to supply power to lower 3 IGBTs and their surrounding circuits and 3 independent power supplies to drive the top portion. However, in a small capacity inverter, one power supply can satisfy all the power needs by using a bootstrap circuit. The gate drive in the inverter, herein, does not need a separate photo-coupler or similar level shifts. However, if a general gate drive is used, a photo-coupler or similar level shift circuit must be used to provide signal to the top part of the gate drive.

#### 5.2 Gate Resistance Calculation

The inverter is assumed to operated with a 10k[HZ] basic PWM frequency. 300[V] for the DC link voltage, 2[A] operating current, 200[mA]/420[mA] source/sink current for maximum drive capacity of the gate drive output used and15[V] for the maximum gate drive voltage have been decided. The stray inductance, which increased slightly due to the DC link current detection resistance in the actual inverter, was measured at 200[nH]. Considering the worst case conditions, the inverter designed did not use a non-inductive resistance for the detection resistance so the stray inductance became much larger than normal. Normal stray inductance is measured below 90[nH]. The stray inductance in the circuit can be roughly estimated by measuring the short circuit current slope and the voltage across the component. The minimum gate

resistance can be calculated based on equation (1) and the above conditions.

$$R_{ON}^{MIN} = \frac{15}{0.2} = 75[\Omega] \text{ and } R_{OFF}^{MIN} = \frac{15}{0.42} = 35.71[\Omega]$$

(12)

The turn on and off resistances are both lower than  $100[\Omega]$  accounting for the turn on loss. The following maximum turn off current can be selected if the surge voltage due to the stray inductance is set to lower than 200[V] taking into account that the IGBT has a internal voltage of 600[V].

$$200 \times 10^{-9} \frac{dt}{di} \le 200$$

$$\frac{dt}{di} \le 1[A/ns]$$

(13)

The maximum turn off resistance based on maximum voltage slope from equation (3) and test waveforms and the Fairchild IGBT databook is presented below.

$$R_{OFF} \le \frac{5[V]}{13E^{-12}[F] \times 3E9[V/sec]} = 128[\Omega]$$

(13)

The appropriate gate resistance can be selected from the above calculation if turn on resistance is set to  $90[\Omega]$  and the turn off resistance is set to  $75[\Omega]$ . In the actual circuit, the gate resistance was set to  $90[\Omega]$  because it was not separated into the turn on and off resistances.

#### 5.3 Parameter Calculation of the Current Detection LPF

The most noise from the power source is in the band of 10[Hz] because the basic frequency of the PWM is10[Hz]. Therefore, the short circuit current detection filter or the over-current detection filter in figure 3.2 must have stop bands of less than 10[kHz]. If the filter pass band is too narrow, all the noise is eliminated, but the filter quick response characteristic falls, which has a negative effect on the circuit operation. If the -3[dB] frequency of the short circuit current detection circuit is changed to 1k[Hz], the noise reduces from 10k[Hz] to -20[dB] and can be effectively eliminated. However, it many not be possible to protect the IGBT if there is a short circuit current because the response is too slow. Therefore, to make the the filter respond faster , the filter performance must sacrificed. By making the -3[dB] frequency to 6k[Hz], an appropriate response and filter effect were obtained. The over-current detection circuit must be slower than the short circuit current filter speed, which is determined by the slope of the overall current. When the inverter is attached with a motor, an actual load, and tested, the slope of the current becomes about 2.3[A/ms] with only the lower part turned off and it takes about 3[ms] to drop from 7[A] to 0. To reduce the current ripple, the IGBT should be turned on again before the current becomes 0 and the filter frequency of -3[dB] should be set to 400[Hz]. The following equation can be derived using the results from above.

$$\frac{1}{R_{F1}C_{F1}} = 800\pi \text{ [Rad/s]}$$

(14)

$$\frac{1}{R_{F2}C_{F2}} = 12000\pi \text{ [Rad/s]}$$

(15)

If  $C_{F1} = C_{F2} = 0.1[\mu F]$  is set,  $R_{F1} \cong 4k[\Omega]$ ,  $R_{F2} \cong 260[\Omega]$ .

#### 5.4 Calculation of the Parameters for the Short Circuit Current Detection Circuit

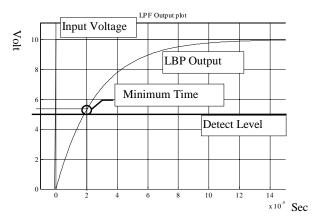

10V is detected when the maximum short circuit current of 20[A] at the 15[V] gate voltage flows because a 0.2[] detection resistance was used . The figure below shows the operation waveform of the short circuit current filter when the starting current of the short circuit current circuit operation is set to 10[A].

Figure 5.2 Input and Output Waveform of the LPF

Because the voltage across the detection resistance with a short circuit current increases as a step wave as shown in the above figure, the short circuit protection must start before the output voltage of the LBP, which was designed in Section 5.3, reaches approximately 5.4[V]. Furthermore, if the amplifier gain is set to 1 and the cutoff operation is executed when the amplifier output becomes 5[V], the IGBT can be protected without any damage. Even if the IGBT current was to increase slowly and exceed 10[A], the IGBT can be protected

because the protection starts at 10[A].

#### 5.4 Parameter Calculation for the Over-current Detection Circuit

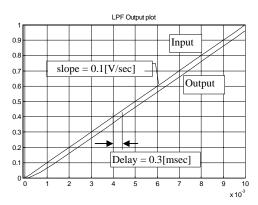

Most over-currents in the inverter, which drives the motor, flow through the motor. Therefore, depending on the load conditions, the slopes of the almost all the current change and can be calculated through the circuit equation or through direct testing. The rising slope of the load current was obtained through testing in this application note. The test consisted of applying a single pulse having a width with low duty to the motor initially and examining the voltage and current waveforms. At this time, the motor must not be operating and the applied pulse should be made low as it can be so that motor demagnetizing due to an over-current does not occur. The maximum slope of the current obtained from testing is 5[A/msec]. Consequently, the slope of the voltage across the detection resistance is 0.1[V/msec] and the output waveform from the filter with this slope as input is shown in the figure below.

#### Figure 5.3 Input and Output Waveform of the LPF

The filter delay time is about 0.3[msec] so  $T_{DOFF}$  is set to about 0.3[msec]. However,  $T_{DOFF}$  becomes much longer because the gate voltage is not dropped to 0[V] immediately but maintained at an appropriate voltage of 5~6[V]. Consequently, we know that it was designed well because the IGBT turns on and off repeatedly at lower than 3[kHz] without straining the IGBT too much. Therefore, if the amplifier gain is 3 times and the comparison level of the over-current comparator is set to 4.0[V], the current can be limited to around the load current of 7[A].

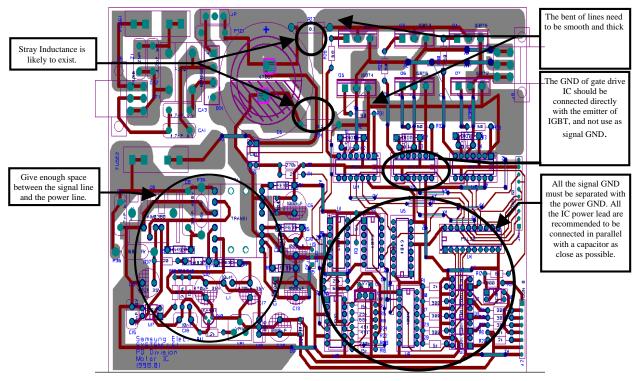

### 5.5 PCB Design Cautions

Though the circuit design is important in the inverter design, what is more important is the art work which moves the circuit to the actual PCB. Though the circuit design may be perfect but, if it was designed without giving special attention to the art work, the circuit could malfunction during actual operation due to an unforeseen noise. The artwork must be carefully designed to prevent circuit damage due to large power when the circuit malfunctions. There is not much theory behind the artwork production, but it does have elements that depend on experience. General items for caution when producing the artwork and items that must be executed in the inverter are listed in this section.

- 1) If possible, separate the gate drive IC's GND from the general analog IC's GND. If this is not possible, do not mix these two lines and use them carelessly.

- 2) Must attach good 0.1[F] capacitors in parallel between the IC power supply V<sub>CC</sub> containing the gate drive IC and the GND.

- 3) The lower gate drive should be separated from the circuit power supply GND using a photo-coupler etc. If not, it should be directly connected to each of the IGBT emitters.

- 4) The closed loop of the line must be avoided as possible.

- 5) A high voltage point and the signal line should be kept far apart whenever possible. If this is difficult, they should be appropriately separated.

- 6) A signal line with little current should be kept far apart from the power line. The IC power supply with this signal as input and output should be directly connected the voltage source.

- 7) When winding the transformer which disconnects the power source, the area where the windings overlap should be minimized in order to reduce the capacitance. If the secondary side of the transformer has capacitance, surge current can pass through due to the sudden voltage change via the transformer.

- 8) The stray inductance should be minimized at the block connecting the DC link capacitor to the IGBT. Therefore, the connection line in this block should make a strong connection and not be bent over 45°.

- 9) When inserting the current detection resistance, the connection of the resistance legs should be short to minimize the stray inductance from this resistance.

The figure below outlines the items for caution when moving the circuit diagram in Figure 5.1 to the PCB.

Figure 5.3 The PCB of an actual inverter circuit and the areas for caution

### 6. Conclusion

As IGBTs with the advantage of the MOSFET and TR are becoming widespread, they are being used in large capacity to small capacity inverters. The IGBT that Fairchild is manufacturing boasts the world's best features in many aspects. This application note details a method of designing an inverter at low cost using the Fairchild IGBT as an output component. To promote the superior features of the Fairchild IGBT, which is not widely known, the inverter design appropriate for the IGBT inherent features is presented. Furthermore, everything from design to artwork in the designing of an actual inverter is covered in detail so that anyone could design the inverter just with this application note.

Though this application note deals with the small capacity inverter design, the gate selection method in Section 2 or the protection circuit configuration method in Section 3, which is common to all inverter designs, can be used as a valuable reference.